The development of two-dimensional (2D) semiconducting materials has opened up a new realm of possibilities for ultra-thin and tunable electronic components. These materials possess distinct optoelectronic properties that offer potential advantages over traditional bulk semiconductors. However, one of the main challenges in utilizing 2D materials for transistor applications has been effectively interfacing them with gate dielectrics. Interfacial traps have often degraded transistor performance, hindering their widespread adoption in electronic devices.

Recently, researchers from King Abdullah University of Science and Technology (KAUST), Soochow University, and other institutions worldwide introduced an innovative approach to address this challenge. Their proposed design, detailed in a paper published in Nature Electronics, involves the use of hexagonal boron nitride (h-BN) dielectrics and metal gate electrodes with a high cohesive energy. This novel combination aims to optimize the performance of transistors based on 2D semiconductors.

First author of the paper, Yaqing Shen, highlighted the discovery that platinum (Pt) as an anode led to decreased dielectric breakdown in the h-BN stack. Building on this initial finding, the research team conducted experiments and observed that Pt/h-BN gate stacks demonstrated significantly lower leakage current compared to Au/h-BN gate stacks. Moreover, they exhibited a high dielectric strength of at least 25 MV/cm. These results underscored the potential of using chemical vapor deposited h-BN as a gate dielectric in 2D transistors.

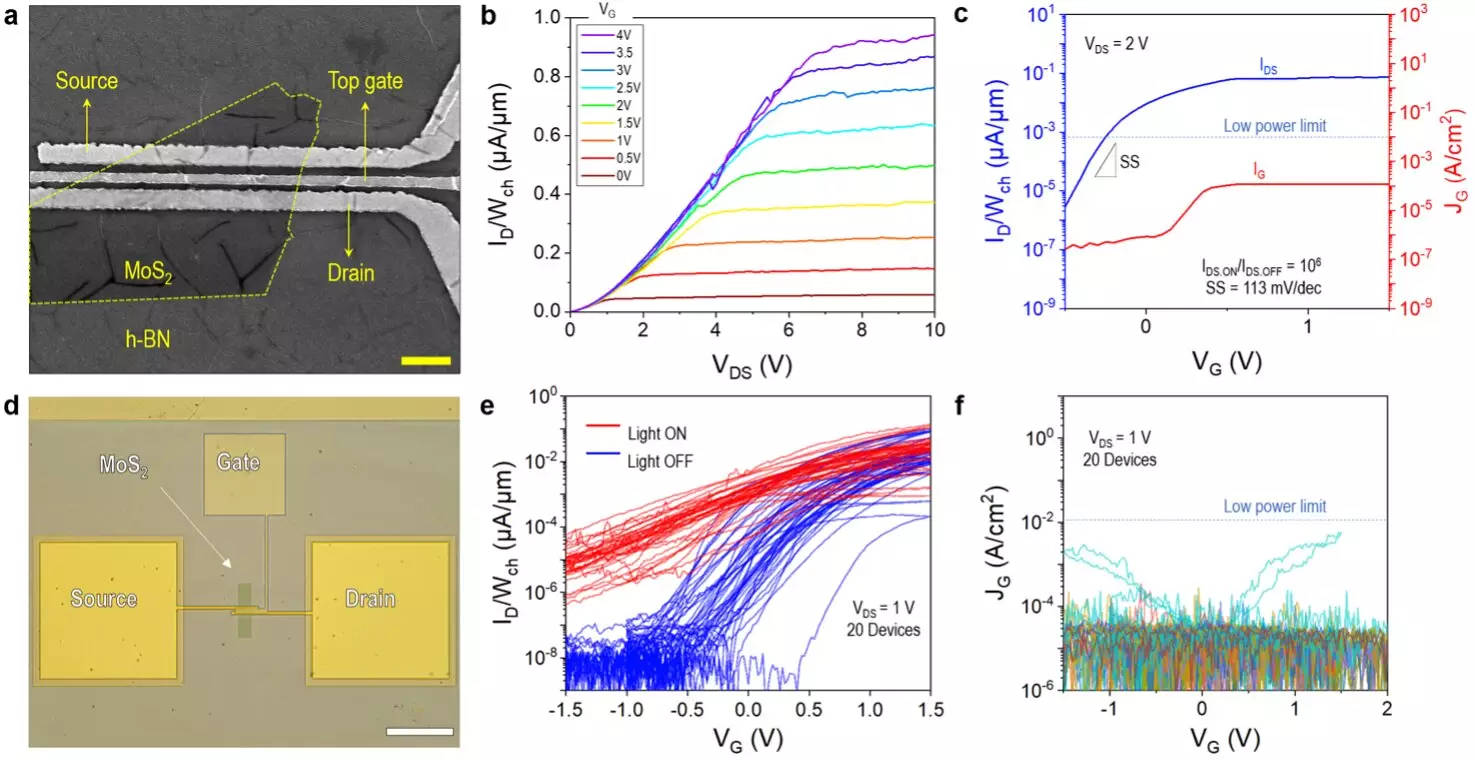

Shen, Prof. Mario Lanza, and their colleagues fabricated over 1,000 devices using h-BN dielectrics. To create transistors with a vertical Pt/h-BN/molybdenum disulfide (MoS2) structure, they followed a meticulous fabrication process. This involved cleaning a SiO2/Si substrate, patterning source and drain electrodes (Ti/Au), transferring MoS2 onto the electrodes to form the channel, and depositing CVD h-BN film over the structure through wet transfer. The final step included patterning the Pt gate electrode using electron beam lithography and depositing it via e-beam evaporation.

The clean van der Waals interface between MoS2 and h-BN in the team’s transistors significantly improved their reliability and performance by minimizing defects and enhancing gate control. Contrary to previous beliefs about CVD h-BN, the researchers demonstrated that selecting the right metal electrodes, such as Pt and tungsten (W), enabled effective use of h-BN as a gate dielectric in 2D transistors. This breakthrough could pave the way for the fabrication of reliable solid-state microelectronic circuits and devices using 2D materials.

The research team’s successful approach to fabricating transistors based on 2D semiconductors holds great promise for the future. By reducing leakage currents and achieving a high dielectric strength, their work sets the stage for further advancements in the field. As other research groups explore similar approaches and materials, the development of highly performing 2D semiconductor-based devices may become more widespread. The next phase of research will focus on developing ultra-small, fully 2D transistors to contribute to the extension of Moore’s Law.

The innovative use of h-BN dielectrics and high cohesive energy metal gate electrodes represents a significant leap forward in the optimization of 2D semiconductor materials for transistor applications. This research opens up exciting possibilities for the future of electronic devices and solid-state microelectronics, laying the foundation for continued advancements in the field.

Leave a Reply